Journal of Optoelectronical Nanostructures Round Water Strengt SCIENTICS

Spring 2018 / Vol. 3, No. 2

# Effects of the Channel Length on the Nanoscale Field Effect Diode Performance

Arash Rezaei<sup>\*,1</sup>, Bahram Azizollah-Ganji<sup>1</sup>, Morteza Gholipour<sup>1</sup> <sup>1</sup>Department of Electrical & Computer Engineering, Babol Noshirvani University of Technology, Babol, Iran.

(Received 7 Mar. 2018; Revised 26 Apr 2018; Accepted 17 May 2018; Published 15 Jun. 2018) **Abstract:** Field Effect Diode (FED)s are interesting device in providing the higher ON-state current and lower OFF–state current in comparison with SOI-MOSFET structures with similar dimensions. The impact of channel length and band-to-band tunneling (BTBT) on the OFF-state current of the side contacted FED (S-FED) has been investigated in this paper. To find the lowest effective channel length, this device is simulated with 75, 55 and 35 nm channel length and the results obtained are presented in this article. Our numerical results show that the  $I_{ON}/I_{OFF}$  ratio can be varied from  $10^4$ to  $10^0$  for S-FED as the channel lengths decrease. We demonstrate that for channel lengths shorter than 35 nm by considering the Band-to-Band tunneling model, the S-FED device does not turn off.

## Keywords: Field Effect Diode (FED), Side Contacted FED (S-FED), Band-To-Band-Tunneling (BTBT), Ion/IoFF Ratio.

# **1. INTRODUCTION**

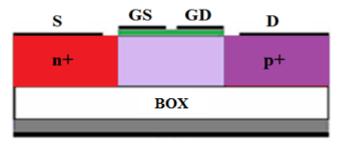

As the scaling of Cmos transistor extends to the nano-scale regime, the performance of the device degrades mainly because of short-channel effects that arise due to weakened gate control [1-3]. Hence, in recent years, new devices have been proposed on a nanoscale. One of these devices is the Field Effect Diode (FED), whose physical structure is depicted in Fig. 1 The structure of FED is similar to that of the conventional MOSFET, with the exception of oppositely doped source and drain regions and also the configuration of the gates. This device was first proposed in 1996 [4].

<sup>\*</sup> Corresponding author. E-mail: arashrezaei92@yahoo.com

Fig. 1. Schematic of the FED structure

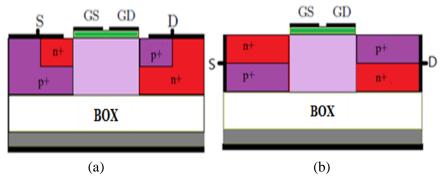

The FED has a higher current than the MOSFET, and a lower leakage current. Therefore, the ION / IOFF ratio, which is one of the most important parameters in digital applications, is more in this device than field-effect transistors with similar dimensions [5, 6]. Field effects diodes have many applications such as ESD protectors [7, 8] and memory cells [9, 10], and can also be used to design integrated circuits [11,12]. As the channel length is scaled below 100 nm, the off-current of regular FEDs increases. To overcome this problem, modified FED (M-FED) (Fig. 2(a)) and side-contacted FED (S-FED) (Fig. 2(b)) structures have been recently proposed [13, 14].In this structure, there are regions in the source and drain areas called reservoir. These introduced regions assist nanoscale FEDs to be turned OFF. The reason the reservoirs are used in nanosized FEDs is that, when the device is off, the carriers that enter from drain and source into the channel are injected into opposite channel sides before annihilation.

Fig. 2. Schematic cross-section of (a) M-FED and (b) S-FED

When channel length decreases in these devices, the tunneling current in the channel is increased and the performance of the field effect diode is disrupted. In this paper, the effect of the channel length on the electrical characteristics and Energy Levels of S-FED is investigated and also compared.

#### 2. DEVICE STRUCTURE

A FED is a structure with two gates over its channel called GS and GD (see Fig. 1) and oppositely doped source and drain regions. The gate contacts of FEDs can be biased such that either a p-n or n-p channel replaces the lightly doped or intrinsic region between the source and drain areas. Based on the gate, source, and drain voltages, the source/channel/drain areas act as n+-n-p-p+ and n-+p-n-p+ structures, respectively. Fig. 1 shows a regular FED based on a SOI structure, where the source and the drain have n-type and p-type doping, respectively. This FED will be in the ON-state if positive and negative voltages are applied to GS and GD, respectively. By just reversing the gate-voltage polarities, the device will be turned off. In the OFF-state, the device has a structure similar to a silicon-controlled rectifier (n-p-n-p). However, as the channel length shrinks below 100 nm, regular FEDs cannot

be turned off [15]. To suppress this problem, M-FEDs have been proposed [15]. In this structure, oppositely doped regions called reservoirs are introduced to the source and drain areas

of regular FEDs (see Fig. 2(a)), where they assist the gate contacts to accumulate more holes and electrons under GS and GD, respectively, and induce a larger surface potential. In other words, in the OFF-state, the excess minority carrier injection takes place across the forward-biased n+-p (source side) and n-p+ (drain side) junctions, causing an increase in the electron and hole concentrations in the p-region (under GS) and the n-region (under GD), respectively. This increase in the electron and hole concentrations obstructs the formation of a reverse-biased p-n junction in the channel. Therefore, to achieve a proper OFF-state current, excess electrons and holes under GS and GD should be reduced. The reservoirs connect the p-region under GS to the source and the n-region under GD. As a result, the forward bias of the n+-p and n-p+ junctions decreases, and the carrier injection into the channel is reduced. In a forward-biased FED, the drain voltage and the neighboring gate have opposite polarities; therefore, pinchoff does not occur in FEDs, and they do not suffer from hot-electron effects, unlike short-channel FETs [4, 16].

To make the fabrication of these devices more feasible, we propose an S-FED. As shown in Fig. 2(b), side contacts are created by utilizing trench technology. Creating side contacts to the source and drain areas can be performed by reactive ion etching and using an oxide layer as an etch stop.

#### 2. RESULTS AND DISCUSSION

In this section, the results of the simulation performed by the ATLAS simulator are examined [17]. We have solved the poisson and continuty equations to obtain the electrical characteristics of the FED, including I-V characteristics and carrier concentrations under each gate.

The FED operation can be explained in terms of a pin diode in which the potential in its intrinsic region is controlled by two gates over the channel. In the side-contacted FED (Fig. 2(b)), the source region is n-type with a donor density  $1 \times 10^{21}$  cm<sup>-3</sup>, drain doping is p-type with  $1 \times 10^{21}$  cm<sup>-3</sup> density, and the so-called intrinsic channel is actually doped with donor type impurities to  $1 \times 10^{14}$  cm<sup>-3</sup>. The gate oxide thickness of 1 nm and a device width are 1 um. The depths of reservoirs and source/drain regions are 50 and 25 nm, respectively. These values and other structural parameters are those employed in [13, 14].

The BTBT model and Shockley–Read–Hall (SRH) model are especially needed for accurate estimation of the leakage currents. The mobility models which account for the lattice scattering, impurity scattering, conmob, field-dependent mobility, carrier–carrier scattering and impurity clustering effects at high concentration are employed. For the accuracy of the ON-current, mobility degradation due to the high transverse electric field is considered.

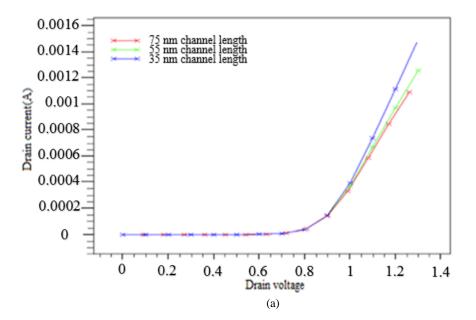

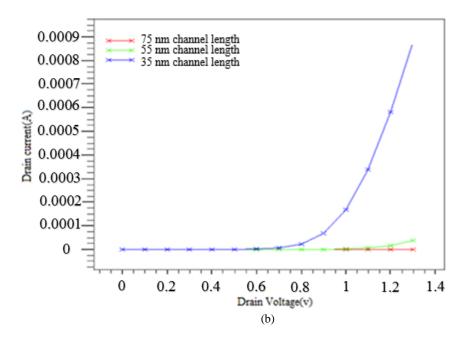

The output characteristics of S-FED structures as a function of the Channel Length are compared in Fig. 3 in the (a) on and (b) off state. As seen in this figure, by decreasing the length of the channel, the on and off current will be increases. In the other words, as Channel Length decreases, The tunnel flow in the channel increases is due to the closeness of the source and drain area.

Fig. 3. Output characteristics of the S-FED as a function of the channel length in the (a) ON and (b) OFF state

As a result, for the channel lengths shorter than 35 nm, S-FED cannot be turned off. However, S-FED device suffers from an increase in  $I_{OFF}$  if channel length is scaled.

Table I shows a comparison between the S-FED structure with similar dimensions for channel length of 35. 55 and 75 nm, taking into account the tunneling phenomenon.

TABLE I

Comparison of simulation results of S-FED structure for channel length 35, 55 and 75 nm, Vd

= 1.3v, Vg = 1v and considering the tunneling phenomenon

|        |                |                 | 01               |                      |

|--------|----------------|-----------------|------------------|----------------------|

| Device | Channel length | I <sub>ON</sub> | I <sub>OFF</sub> | $I_{ON} / I_{OFF}$   |

| S-FED  | 75 nm          | 1.05 mA         | 90.8 nA          | 1.15×10 <sup>4</sup> |

| S-FED  | 55 nm          | 1.25 mA         | 39 uA            | 32.05                |

| S-FED  | 35 nm          | 1.5 mA          | 0.87 mA          | 1.72                 |

Spring 2018 / Vol. 3, No. 2

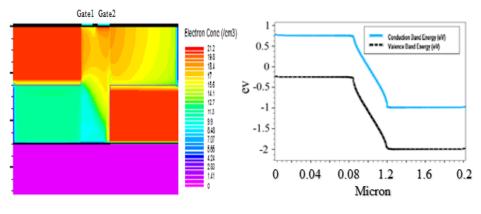

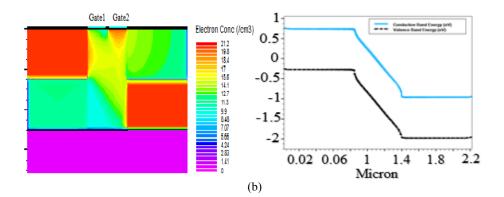

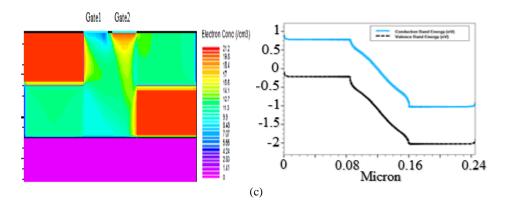

Fig. 4 illustrates the electron density and band diagram at a depth equal to 27 nm at the S-FED device in the OFF-state for 35, 55 and 75 nm channel length. Upon scaling electron direct tunneling from source to drain plays a major role in the OFF-state current. It appears that in the S-FED device physics reported in [14] no BTBT has been taken into account.

**Fig. 4.** Electron density and band diagram at a depth equal to 27 nm when the BTBT model is included in (a) the 35 nm channel length S-FED structure and (b) the 55 nm channel length S-FED structure (c) the 75 nm channel length S-FED structure.

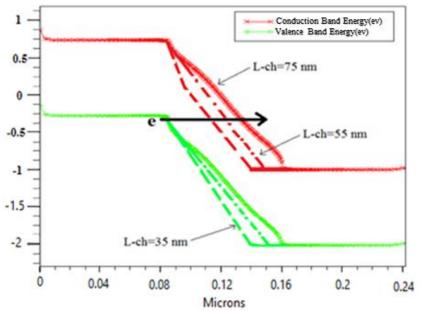

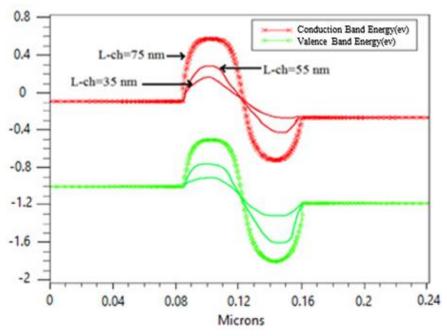

Fig. 5 compares the band diagram at a depth equal to 27 nm when the BTBT model is included for various channel lengths.by decreasing the channel length, the electron direct tunneling from source to drain is increases.

Fig. 5. Energy band diagram taken horizontally across the S-FED at distance 27 nm from the surface when the BTBT model is included

S-FED cannot be turned off for channel lengths equal to 35 nm and the shorter. As a result, OFF-state current is increased noticeably for the 35 nm channel length in comparison with that 55 and 75 nm channel length of the S-FED. Figure.6 shows the changes in energy levels at 2 nm below the gate in off state. As expected, by decreasing channel length, the potential dam is reduced.

Fig. 6. Energy band diagram taken horizontally across the S-FED a distance 2 nm from the surface when the BTBT model is included

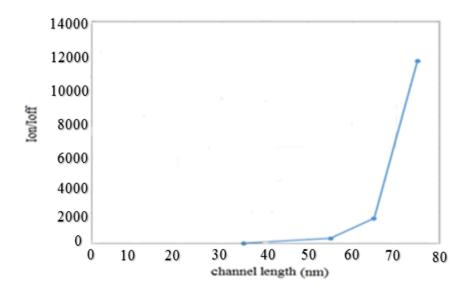

Figure. 7 compares the  $I_{ON}/I_{OFF}$  ratio as a function of channel length for S-FED. Fig.7 illustrates that by decreasing the channel length and considering the tunneling phenomenon, the  $I_{ON}/I_{OFF}$  ratio decreases.

Fig. 7.  $I_{ON}/I_{OFF}$  ratio as a function of channel length for the S-FED

## **5. CONCLUSION**

In this paper, the role of the channel length and band-to-band tunneling (BTBT) on the performance of S-FED is investigated. Simulation results in this paper show that the band diagram of the S-FED device for less than 35 nm channel length is similar to the tunneling diode. Hence electron tunneling from the valence band into the conduction band is formed. As a result, additional electron hole pairs are generated and contribute to the OFF-state current. Therefore, BTBT increases the OFF-state current of the S-FED device. The characteristic of the voltage-current and energy levels of this structure was studied for 75 nm, 55 nm and 35 nm channel length. Our studies indicate that by decreases the channel length, the  $I_{ON}/I_{OFF}$  ratio can be varied from  $10^4$  to  $10^0$  for S-FED. Therefore that for channel lengths shorter than 35 nm by considering the Band-to-Band tunneling model, the S-FED device does not turn off.

#### REFERENCES

B. Yu, L. Wang, Y. Yuan, P. M. Asbeck and Y. Taur. *Scaling of Nanowire Transistors*. IEEE Transactions on Electron Devices. 55(11) (2008, Nov.) 2846-2858. Available: <u>https://ieeexplore.ieee.org/document/4668604</u>

G. Joshi and A. Choudhary. Analysis of short channel effects in nanoscale MOSFETs. International Journal of Nanoscience 10(01n02) (2011) 275-278. Available: <u>http://www.worldscientific.com/doi/abs/10.1142/s0219581x11007910</u>

- [2] A.Kranti, T. M. Chung, and J.-P. Raskin. *Gate length scaling and microwave performance of double gate nanotransistors*. International Journal of Nanoscience 4(05n06) (2005) 1021-1024.

Available: https://www.worldscientific.com/doi/abs/10.1142/S0219581X05004005

- [3] F. Raissii. A brief analysis of the field effect diode and breakdown transistor. IEEE Transactions on Electron Devices. 43(2) (1996, Feb) 362-365. Available: https://ieeexplore.ieee.org/abstract/document/481742

- [4] I.Sheikhian and F.Raissi. *High-speed Digital family using Field Effect Diode*. ELECTRONICS LETTERS. 39 (4) (2003) 345-347. Available: <u>https://ieeexplore.ieee.org/abstract/document/1184057</u>

- [5] I.Sheikhian and F.Raissi. An Improved Differential Comparator with Field Effect Diode Output Stage. Journal of circuts, systems, and computers.14 (5) (2005) 931-937.

Available: http://www.worldscientific.com/doi/abs/10.1142/S0218126605002684

- [6] S. Cao, A. A. Salman, J. –H. Chun, S. G. Beebe, M. M. Pelella and R. Dutton. Design and characterization of ESD protection devices for high-speed I/O in advanced SOI technology. IEEE Trans.Electron Devices. 57(3) (2010) 644-653. Available: <u>https://ieeexplore.ieee.org/abstract/document/5406085</u>

- [7] S. Cao, T. W. Chen, S. G. Beebe and R. W. Dutton, ESD Design chanllenges and strategies in deeply-scaled interated circuits, in Proc. IEEE 2009 Custom Integrated Circuits Conference (CICC), (2009) 681-688. Available: <u>https://ieeexplore.ieee.org/abstract/document/5280727</u>

- [8] M. Amirmazlaghani and F. Raissi, Memory cell using modified field effect diode. IEICE Electronic Express. 6(22) (2009)1582-1586. Available: <u>https://www.jstage.jst.go.jp/article/elex/6/22/6\_22\_1582/\_article/-char/ja</u>

- [9] Yang Y, Gangopadhyay A, Li Q, Ioannou DE, Scaling of the SOI field effect diode (FED) for memory application, in Proc. InSemiconductor Device Research Symposium, (2009) 1-2. Available: <u>https://ieeexplore.ieee.org/abstract/document/5378045</u>

- [10] F. Jazayeri, B. Forouzandeh and F. Raissi, Low-power variable gain amplifire with UGBW based on nanoscale Field Effect Diode, IEICE Electronics Express. 6(1) (2009) 51-57.

Available: <u>https://www.jstage.jst.go.jp/article/elex/6/1/6\_1\_51/\_article/-char/ja</u>

- [11]F. Jazayeri, S. Soleimani-Amori, B. Ebrahimi, B. Forouzandeh, H. R. Ahmadi and F. Raissi. *Pseudo-Linear automatic gain control system based on nanoscale field effect diode and SOI-MOSFET*. Design and Test workshop 2008. (2008). Available: <u>https://ieeexplore.ieee.org/abstract/document/4802487</u>

- [12] I. Sheikhian and F. Raissi, Simulation results for nanoscale field effect diode. IEEE Trans. Electron Devices. 54(3) (2007) 613-617.

Available: <u>https://ieeexplore.ieee.org/abstract/document/4114858</u>

- [13] N. Manavizadeh, F. Raissi, E. A. Soleimani, M. Pourfath, and S. Selberherr. *Performance assessment of nanoscale field-effect Diodes*. IEEE Transactions on Electron Devices. 58(8) (2011) 2378-2384. Available: https://ieeexplore.ieee.org/abstract/document/5779716

- [14] F. Raissi and I. Sheikhian. Nano-scale transistor device with large current handling capability, European Patent EP1 965437 (2008).

Available: <u>https://patents.google.com/patent/EP1965437A1/en</u>

- [15] J. J. Sanchez, K. K. Hsueh, and T. A. Demassa. *Drain-engineered hot-electron*resistant device structure: A review. IEEE Trans. Electron Devices. 36(6) (1989, Jul.) 1125–1132.

Available: https://ieeexplore.ieee.org/abstract/document/24357

- [16] International Device Simulation Software, SILVACO TCAD. (2010).

40 \* Journal of Optoelectronical Nanostructures

Spring 2018 / Vol. 3, No. 2